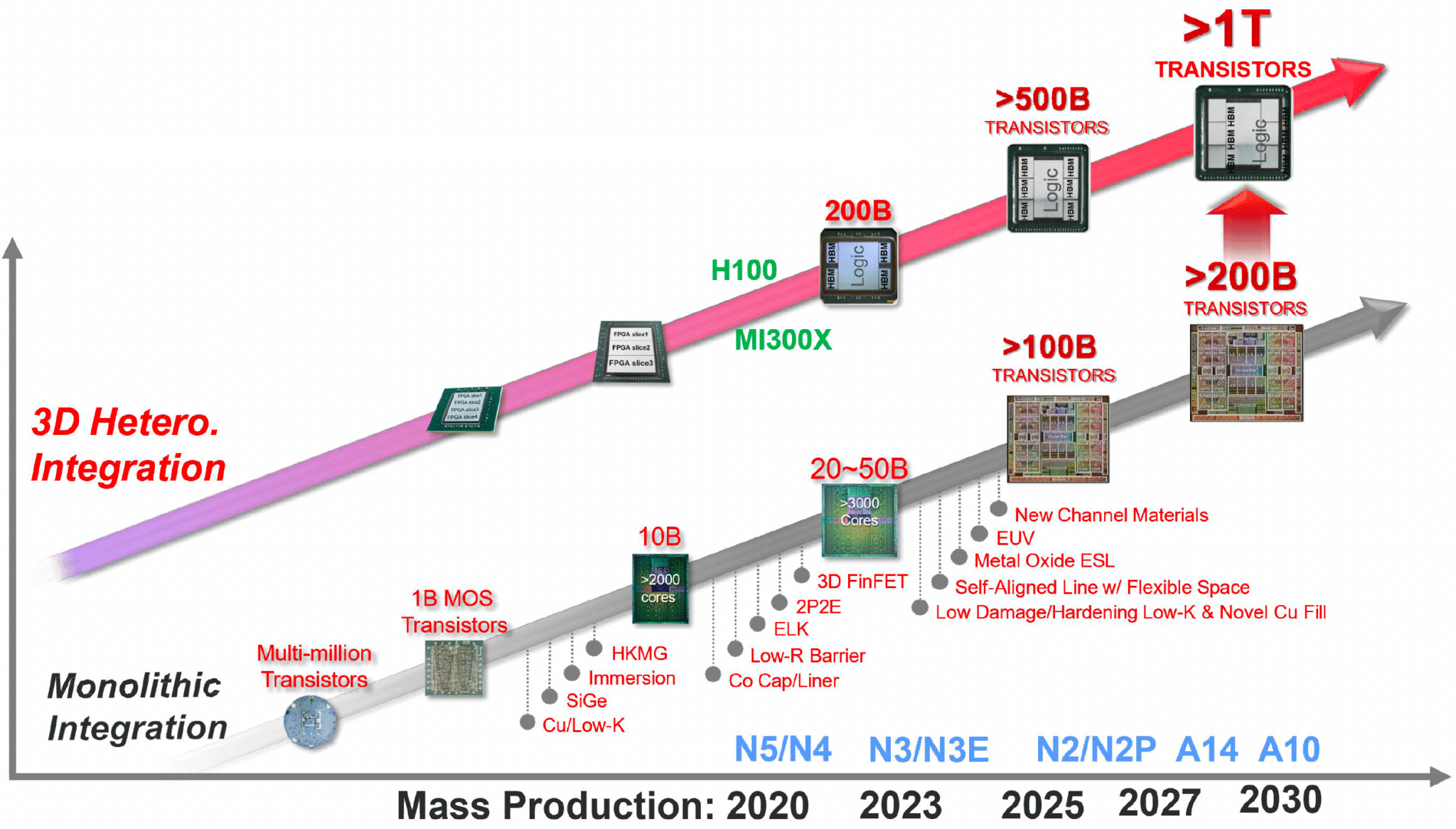

رسمت شركة TSMC مسارًا واضحًا لتقديم حزمة رقاقات ضخمة تحتوي على تريليون ترانزستور، وهو يشبه إلى حد كبير ما كشفت عنه شركة إنتل العام الماضي وأكدته في الآونة الأخيرة.

وتباطأ مستوى تطور دقة التصنيع خلال السنوات الأخيرة إذ يواجه صانعو الرقاقات التحديات التقنية والمالية، وتواجه TSMC الصعوبات ذاتها التي تواجهها الشركات الأخرى.

لكن أضخم مسبك في العالم واثق بأنه سيكون قادرًا على تطوير دقة التصنيع الخاصة به ليحقق مستوى الأداء ومعدل استهلاك الطاقة وكثافة الترانزستور المطلوبة خلال السنوات الخمس أو الست المقبلة عبر دقة تصنيع تبلغ 2 نانومتر، ودقة تصنيع تبلغ 1.4 نانومتر، ودقة تصنيع تبلغ 1 نانومتر.

TSMC تعتقد أنها قادرة على الوصول إلى تريليون ترانزستور من خلال مجموعة ثلاثية الأبعاد من رقاقات السيليكون الصغيرة في حزمة شريحة واحدة، لكن TSMC تعمل أيضًا على تطوير رقاقات تحتوي قرابة 200 مليار ترانزستور في قطعة واحدة من السيليكون.

ولتحقيق هذا الهدف، أكدت TSMC مجددًا أنها تعمل على دقة تصنيع تبلغ 2 نانومتر يرمز لها باسم N2 و N2P، ودقة تصنيع تبلغ 1.4 نانومتر يرمز لها باسم A14، ودقة تصنيع تبلغ 1 نانومتر يرمز لها باسم A10 بحلول عام 2030.

بالإضافة إلى ذلك، تتوقع TSMC حدوث تطورات في تقنيات التعبئة والتغليف (CoWoS، و InFO، و SoIC)، مما يسمح لها ببناء حزم ضخمة متعددة الرقاقات تحتوي على أكثر من تريليون ترانزستور في عام 2030.

وفقًا للصورة التي كشفت عنها TSMC خلال مشاركتها في مؤتمر IEDM، وهو مؤتمر يناقش أحدث التكنولوجيا في مجال تصنيع أجهزة أشباه الموصلات، سيكون هناك رقاقات متجانسة أكثر تعقيدًا تحتوي على أكثر من 100 مليار ترانزستور قريبًا، لكن بناء مثل هذه المعالجات الكبيرة أصبح أكثر تعقيدًا وتكلفة، لذلك تختار العديد من الشركات تصميمات متعددة الرقاقات.

تابعنا